Hat vielleicht jemand schon mal das Problem gehabt, dass ein ankommendes Signal nicht zum richtigen Zeitpunkt ankommt? Z.B. ereignet sich der Übergang eines einkommenden Datensignals quasi gleichzeitig mit dem positiven Übergang eines Systemtaktsignals, zu dem alles in einem entwickelten System gekoppelt ist. Um das einkommende Datensignal zeitlich zu verschieben, kann die Primitive IODELAY2 benutzt werden. Hier wird kurz und übersichtlich beschrieben wie man ein IODELAY2 für die einkommenden Signale verwendet und wie eventuell auftretende Schwierigkeiten berücksichtigt werden können. Dies wird an einem praktischen Beispiel erläutert.

Die Primitive IODELAY2 befindet sich in allen Input-Output-Blocks (IOBs) und kann für einkommende Signale auf zwei (allgemeine) Weisen benutzt werden: für eine konstante oder aber variable Verzögerung des Signals. Die Konfiguration der Primitive wird anhand von, bei der Instantierung übergebenen, Attributen festgelegt. Die Art der Verzögerung eines einkommenden Signals wird mit dem IDELAY_TYPE Attribut angegeben. Für einen variablen Modus kann dieses Attribut entweder VARIABLE_FROM_ZERO oder VARIABLE_FROM_HALF_MAX sein, je nachdem wie lange die Verzögerung von IODELAY2 gleich nach der Kalibrierungsprozedur sein muss. Die Modi mit der konstanten Verzögerung werden durch FIXED oder DEFAULT Werte des IDELAY_TYPE Attributs ausgewählt. Die Modi mit der konstanten Verzögerung benötigen kein CLK Signal.

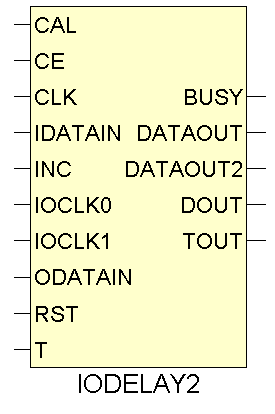

Ohne in die Details der Struktur der Primitive zu gehen, die in UG381 schon gut beschrieben ist, sieht diese IODELAY2 Primitive so aus:

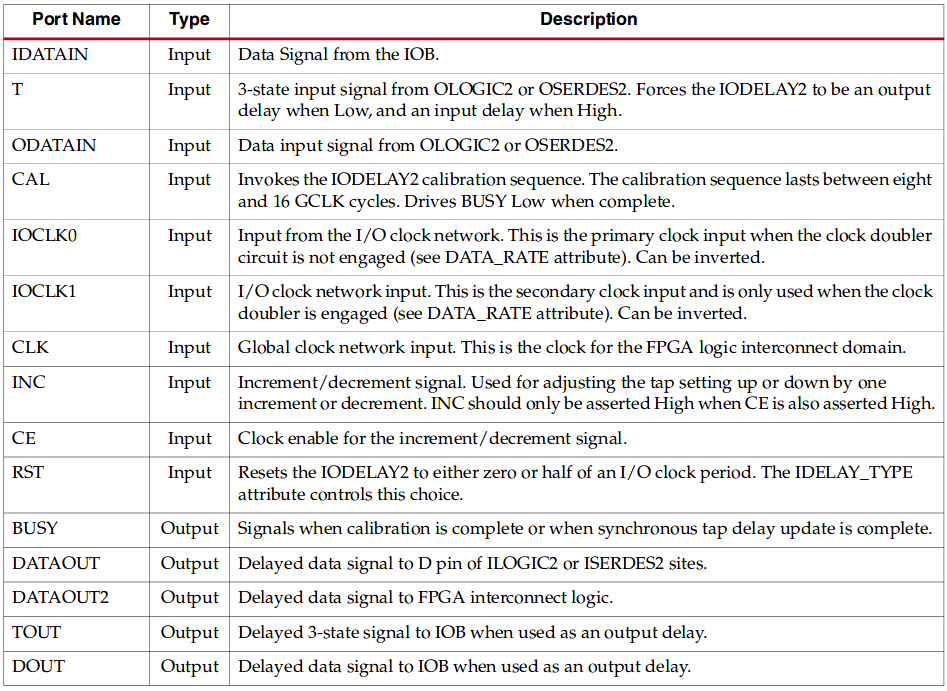

Die Beschreibung der Ein- und Ausgänge der IODELAY2 Primitive findet man in UG381 in der Tabelle 2-8 (Seite 74.):

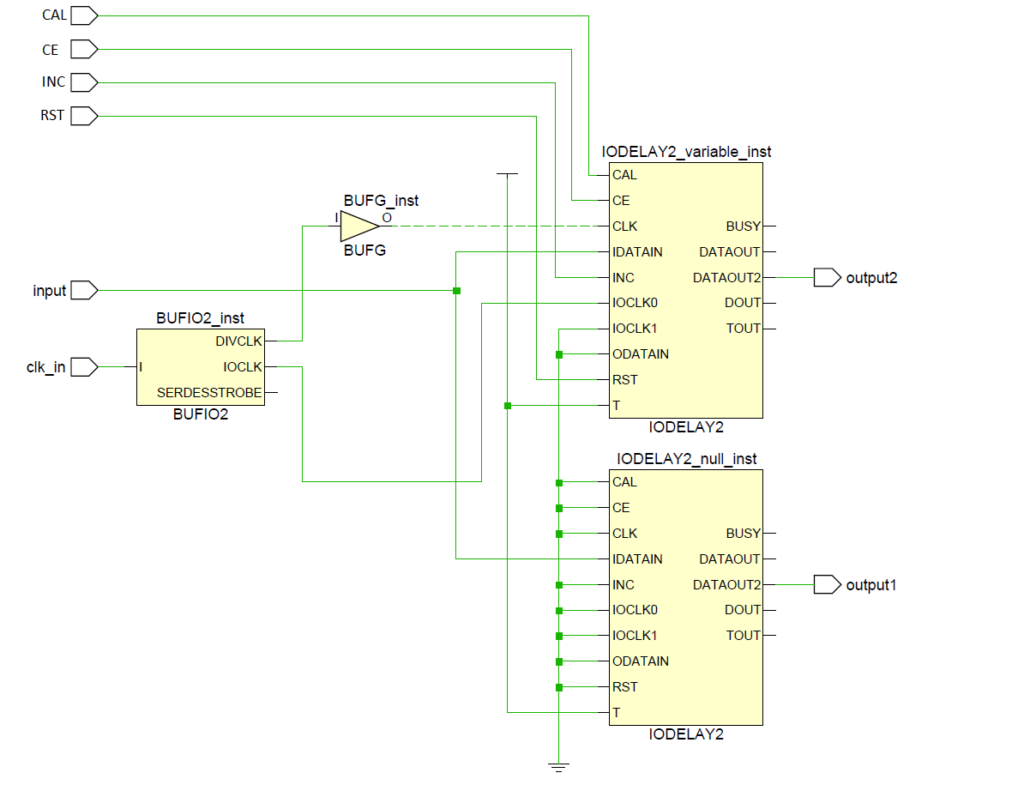

In dem später gezeigten Beispiel wird ein einkommendes Signal durch zwei IODELAY2-Primitiven parallel geleitet. Die erste Primitive befindet sich im DEFAULT Modus, die zweite im VARIABLE_FROM_ZERO Modus. Mit der zweiten der Primitiven kann die Verzögerung des einkommenden Signals auf dem DATAOUT2-Ausgang manuell angepasst werden.

Die Verzögerung kann maximal 255 sogenannte „Taps“ betragen. Wie lang die Taps sind, wird in Dokumentation von Xilinx nicht direkt angegeben. Die Länge eines Taps hängt von der Temperatur und der Versorgungsspannung ab. So wie ich es aus der Dokumentation und Foren verstanden habe, kann man die Dauer eines Taps mit 40ps abschätzen. Die Anzahl der Taps einer IODELAY2-Primitive, die sich im variablen Modus befindet, kann manuell in- und dekrementiert werden. Dafür benutzt man die INC und CE Eingänge der IODELAY2 Primitive (siehe Tabelle). Wenn man die gesamte Verzögerung z.B. inkrementieren will, setzt man erst das INC-Signal zu „1“ und danach setzt man das CE-Signal zu „1“. Genauso verfährt man, um die Verzögerung zu verkürzen, allerdings muss natürlich das INC-Signal auf „0“ gesetzt werden. Wie ich (praktisch) herausgefunden habe, entspricht die Anzahl der In- oder Dekrementschritte der Anzahl der positiven Flanken des CE-Signals. Das heißt, wenn z.B. das INC-Signal positiv ist, verursacht ein positiver Übergang des CE-Signals das Hinzufügen eines Taps zu der gesamten Verzögerung, egal wie viele Taktperioden danach das CE-Signal positiv bleibt. Die letzte wichtige Sache: um die normale Funktion eines IODELAY2 Primitives im variablen Modus zu ermöglichen, muss die Kalibrierungsprozedur der jeweiligen Primitive durchgeführt werden. Dafür muss der Zustandsautomat nach einem Reset den CAL-Eingang der Primitive auf „1“ einmal setzen.

Im folgenden Video ist zu sehen, wie die Signale an den beiden Ausgängen aussehen: